ARMv8(aarch64)页表建立过程详细分析_aarch64 页表-CSDN博客

【原创】(一)ARMv8 MMU及Linux页表映射 - LoyenWang - 博客园

arm页表

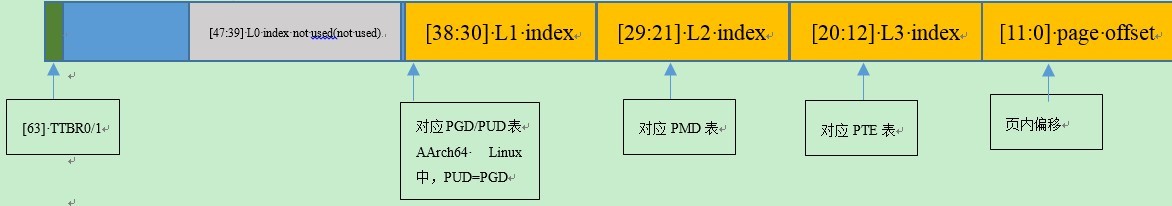

ARMv8架构可以支持48位虚拟地址,并配置成4级页表(4K页),或者3级页表(64K页)。而本Linux系统只使用39位虚拟地址(512G内核,512G用户),配置成3级页表(4K页)或者2级页表(64K页)

用户空间的地址63:39位都置零,内核空间地址63:39都置一,虚拟地址的第63位可以用来选择TTBRx

AArch64Linux内存布局:

| 地址范围开始 | 地址范围结束 | 大小 | 用途 |

|---|---|---|---|

| 0000000000000000 | 0000007fffffffff | 512GB | 用户空间 |

| ffffff8000000000 | ffffffbbfffcffff | ~240GB | vmalloc区域 |

| ffffffbbfffd0000 | ffffffbcfffdffff | 64KB | 守护页 |

| ffffffbbfffe0000 | ffffffbcfffeffff | 64KB | PCI I/O空间 |

| ffffffbbffff0000 | ffffffbcffffffff | 64KB | 守护页 |

| ffffffbc00000000 | ffffffbdffffffff | 8GB | vmemmap区域 |

| ffffffbe00000000 | ffffffbffbffffff | ~8GB | 守护页和未来vmemmap区域 |

| ffffffbffc000000 | ffffffbfffffffff | 64MB | 模块区域 |

| ffffffc000000000 | ffffffffffffffff | 256GB | 内存(保留或未分配) |

aarch64虚拟地址

4K页时的虚拟地址

64K页时的虚拟地址

- PGD全局页表字典

- PTE页表项

- PMD 中间页表字典

TLB

Translation lookaside buffer,即旁路转换缓冲,或称为页表缓冲;里面存放的是一些页表文件(虚拟地址到物理地址的转换表)。又称为快表技术。如果匹配到逻辑地址就可以迅速找到页框号(页框号可以理解为页表项),通过页框号与逻辑地址的后12位的偏移自合得到最终的物理地址。如果没在TLB中匹配到逻辑地址,就出现TLB不命中(TLB Misss),需要通过常规的页表查询。如果TLB足够大,那么这个转换就会变得迅速。但是事实是TLB的容量非常小,一般都是几十项到几百项不等。

在有些的处理器架构中,为了提供效率,还将TLB进行分组,以X86架构为例,一般都分为以下四个组:

第一组:缓存一般页表(4KB页面)的指令页表缓存(Instruction-TLB)

第二组:缓存一般页表(4KB页面)的数据页表缓存(Data-TLB)

第三组:缓存大尺寸页表(2MB/4M页B面)的指令页表缓存(Instruction-TLB)

第四组:缓存大尺寸页表(2MB/4MB页面)的数据页表缓存(Data-TLB)

举一个例子:假设一个应用程序需要使用8KB的物理内存,如果使用常规页(4KB)并且使TLB总能命中,那么至少需要在TLB表中存放两个表项,在这种情况下,只要寻址的内容都在该内容页内,那么只要两个表项就足够了。如果该应用程序需要使用512个内容页也就是2MB大小,那么需要512个页表表项才能保证不会出现TLB不命中的情况。但是TLB容量有限,随着程序的变大或者使用内存的增加,那么势必会增加TLB的使用项,最后导致TLB出现不命中的情况。此时,大页的优势就显示出来了,如果使用2MB作为分页的基本单位,那么只需要一个页表项就可以保证不出现TLB不命中的情况;对于消耗内存以GB(2^30)为单位的大型程序,可以采用1GB为单位作为分页的基本单位,减少TLB不命中的情况。

页表建立过程

1 | /* |